# EPC7009L16SH Radiation-Hardened GaN Gate Driver Datasheet

## **Features**

- Compatible with all EPC Space Discrete eGaN<sup>®</sup> products

- Single GAN Gate Driver Integrated Circuit

- Independent Pull-Up and Pull-Down gate drive outputs

- Capable of Driving 5000 pF+ Loads

- High Speed Capability: 3.0 MHz+

- 3 V Logic-Compatible Input control

- Non-Inverting and Inverting Logic Inputs

- 10 V Supply for Interface to Legacy PWM Controllers

- Hermetic Ceramic QLCC SMT Package

- Extremely Small Size: 0.228 x 0.183 x 0.085 inches

- Guaranteed Total Ionizing Dose:

- Rated to 1000 krad(Si) for HDR (50-300 rad(Si)/s

- Rated to 100 krad(Si) for LDR (100 mrads(Si)/s

- Single Event:

- SEE immunity for LET of 84 MeV/mg/cm<sup>2</sup>

- Neutron Fluence:

- Maintains Specification up to 1 x 10<sup>15</sup> N/cm<sup>2</sup>

### Applications

- DC-DC conversion

- Satellite Electrical

- Power Switches/Actuators

- Motor Drivers

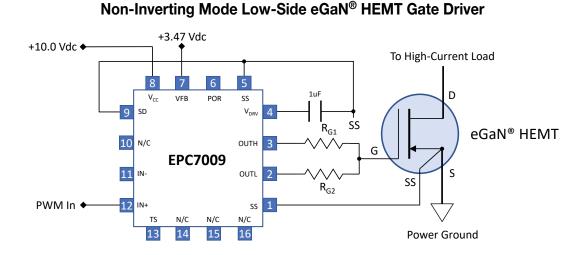

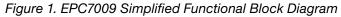

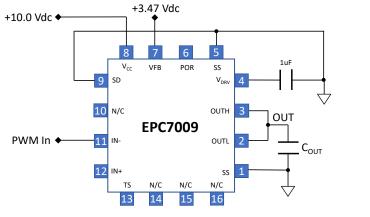

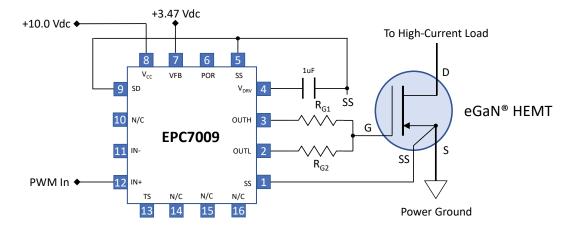

# **Typical Application Circuit**

# EPC7009L16SH

Radiation-Hardened Single Output GaN Gate Driver Monolithic IC

## Description

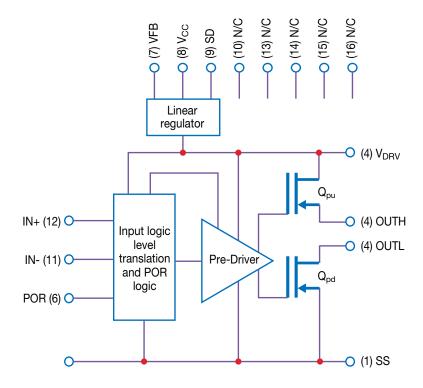

The EPC7009L16SH is a radiation hardened, high-speed gate-driver, implemented as an integrated circuit (IC) using EPC's proprietary eGaN<sup>®</sup> technology. The EPC7009 GaN IC contains an on-chip 10 V to 5.25 V linear regulator, under-voltage lockout protection and independent pull-up and pull-down outputs to both optimize and simplify the gate-drive to an external GaN FET. The IC is packaged in an innovative, space-saving hermetic 16-pin SMT package.

ISPACE

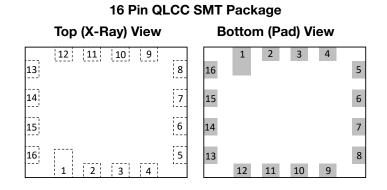

#### EPC7009L16SH Piinout

#### EPC7009L16SH Pin Descriptions and Functionality

| Pin # | Pin<br>Name | (I)nput,<br>(O)utput,<br>(P)ower | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SS          | Ρ                                | Gate driver ground return that is connected to the "Source Sense" (SS) pad on EPC Space eGaN HEMTs. Keep the connection from the SS pin to the Source pad as short as possible. The substrate of the IC is also connected to the SS pin.                                                                                                                                                                             |

| 2     | OUTL        | 0                                | Gate driver high peak current pull-down output. When ON, the OUTL output is pulled down to the SS potential. In most applications this pin should be connected directly to the gate pad of EPC Space eGaN HEMTs. Keep the connection from the OUTL pin to the Gate pad as short as possible.                                                                                                                         |

| 3     | OUTH        | 0                                | Gate driver high peak current pull-up output. When ON, this output is pulled up to the VDRV potential. A low value resistor (10 W, maximum) may be connected in series with the OUTH pin and the Gate pad of EPC Space eGaN HEMTs in order to slow down the rise time of the HEMT being driven. Keep the connection from the OUTH pin (and through the optional gate resistor) to the Gate pad as short as possible. |

| 4     | VDRV        | Р                                | Regulated 5.0 V supply voltage. Connect a 1.0 $\mu$ F, minimum, bypass capacitor from V to SS.                                                                                                                                                                                                                                                                                                                       |

| 5     | SS          | Р                                | Gate driver ground return that is connected to the "Source" pad on EPC Space eGaN HEMTs. Keep the connection from the SS pin to the Source pad as short as possible. The substrate of the IC is also connected to the SS pin.                                                                                                                                                                                        |

| 6     | POR         | I/O                              | Power-On-Reset output. IC is active when POR is logic 0. Connect to SS to disable the POR function. (When POR is logic 1, it will disable the gate driver.)                                                                                                                                                                                                                                                          |

| 7     | VFB         | I                                | Adjustable reference input voltage for linear regulator.                                                                                                                                                                                                                                                                                                                                                             |

| 8     | VCC         | Р                                | External 10 V power supply connection referenced to SS.                                                                                                                                                                                                                                                                                                                                                              |

| 9     | SD          | I                                | Internal linear regulator shutdown input (low ON, high OFF).                                                                                                                                                                                                                                                                                                                                                         |

| 10    | NC          |                                  | No connection                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11    | IN-         | I                                | Negative logic input, level referenced to SS. Output will be high when $IN - \langle V_{IL} \rangle$ with $IN + = V_{DRV}$ . This input has an internal pull-down resistor to SS.                                                                                                                                                                                                                                    |

| 12    | IN+         | I                                | Positive logic input, level referenced to SS. Output will be high when $IN+ > V_{IH}$ with $IN- = SS$ or floating. This input has an internal pull-down resistor to SS.                                                                                                                                                                                                                                              |

| 13    | NC          |                                  | No connection                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14    | NC          |                                  | No connection                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15    | NC          |                                  | No connection                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16    | NC          |                                  | No connection                                                                                                                                                                                                                                                                                                                                                                                                        |

### **Absolute Maximum Rating** ( $T_c = 25^{\circ}C$ unless otherwise noted)

| Symbol                                     | Parameter-Conditions                                      | Value       | Units |

|--------------------------------------------|-----------------------------------------------------------|-------------|-------|

| V <sub>CC</sub> - SS                       | Input Supply Voltage                                      | 16          |       |

| V <sub>DRV</sub> - SS                      | Regulated Gate Driver Voltage                             | 6           |       |

| IN+ - SS,<br>IN SS,<br>SD - SS<br>POR - SS | SS,<br>D-SS Logic Input Voltage Range -1.5 to 6           |             | V     |

| VFB - SS                                   | SS Regulator Feedback Adjustment Voltage Range -1.5 to 6  |             |       |

| TS - SS                                    | Temperature Sensor Resistor Input Voltage Range -1.5 to 6 |             |       |

| T <sub>STG</sub>                           | Storage Junction Temperature Range                        | -55 to +150 |       |

| TJ                                         | Operating Junction Temperature Range                      | -55 to +125 | °C    |

| T <sub>c</sub>                             | Case Operating Temperature Range                          | -55 to +110 | -0    |

| T <sub>sol</sub>                           | Package Mounting Surface Temperature 230                  |             |       |

| ESD                                        | ESD Class Level (HBM)                                     | 1A          |       |

#### **Thermal Characteristics**

| Symbol          | Parameter-Conditions                         | Value | Units |

|-----------------|----------------------------------------------|-------|-------|

| $R_{\theta JA}$ | Thermal Resistance Case-to-Ambient (Note 3)  | TBD   | °C/W  |

| $R_{\theta JC}$ | Thermal Resistance Junction-to-Case (Note 3) | TBD   | C/ W  |

### **OUTL and OUTH Static Electrical Characteristics** ( $T_c = 25^{\circ}C$ unless otherwise noted)

| Symbol                                  | Parameter                                                                                           | Test Condition                                                                           | IS                                                                     | MIN          | TYP         | MAX  | Units |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|-------------|------|-------|

|                                         |                                                                                                     | $V_{DBV} = 5 V_{DC}$ , $IN + = 0.8 V_{DC}$ ,                                             | $T_{\rm C} = 25^{\circ}{\rm C}$                                        |              | 0.05        | 0.1  |       |

| V <sub>OL</sub>                         | OUTL Low-Level Voltage                                                                              | $V_{DRV} = 5 V_{DC}, INV = 0.8 V_{DC},$<br>$I_{OUTL} = 50 \ \mu A \ (Note 1)$            | $\begin{array}{l} T_{C}=-55^{\circ}C\\ T_{C}=110^{\circ}C \end{array}$ |              | 0.05<br>0.1 | 0.15 |       |

|                                         |                                                                                                     | $V_{DBV} = 5 V_{DC}$ , $IN + = 3 V_{DC}$ ,                                               | $T_{\rm C} = 25^{\circ}{\rm C}$                                        | 4.90         | 4.95        |      | V     |

| V <sub>OH</sub> OUTH High-Level Voltage | $V_{DRV} = 5 V_{DC}, \text{ IN}^{+} = 5 V_{DC},$<br>$I_{OUTH} = -50 \ \mu\text{A} \text{ (Note 1)}$ | $\begin{array}{l} T_{C}=-55^{\circ}C\\ T_{C}=110^{\circ}C \end{array}$                   | 4.85                                                                   | 4.90<br>4.90 | 5.00        |      |       |

|                                         |                                                                                                     |                                                                                          | $T_{\rm C} = 25^{\circ}{\rm C}$                                        |              | 0.5         |      |       |

| R <sub>DS(on)</sub>                     | OUTL Pull-Down ON-State Resis-<br>tance (V <sub>DRV</sub> -OUT)                                     | $V_{DRV} = 5 V_{DC}$ , IN+ = 0.8 $V_{DC}$ ,<br>I <sub>OUT</sub> = 0.25 A (Notes 1, 2, 3) | $\begin{array}{l} T_{C}=-55^{\circ}C\\ T_{C}=110^{\circ}C \end{array}$ |              |             |      | Ω     |

|                                         |                                                                                                     | $V_{DRV} = 5 V_{DC}, IN+ = 3 V_{DC},$<br>$I_{OUT} = -0.25 A (Note 1)$                    | $T_{\rm C} = 25^{\circ}{\rm C}$                                        |              | 0.5         |      | 12    |

| R <sub>DS(on)</sub>                     | OUTH Pull-Up ON-State Resis-<br>tance (V <sub>OUT</sub> -SS)                                        |                                                                                          | $\begin{array}{l} T_{C}=-55^{\circ}C\\ T_{C}=110^{\circ}C \end{array}$ |              |             |      |       |

### **IN+/IN- Logic Input Static Electrical Characteristics** (*T<sub>C</sub>* = 25°*C unless otherwise noted*)

| Symbol            | Parameter                        | Test Conditions                                                 | MIN | ΤΥΡ  | MAX  | Units |

|-------------------|----------------------------------|-----------------------------------------------------------------|-----|------|------|-------|

| V <sub>IL</sub>   | Low Logic Level Input Voltage    | V <sub>DRV</sub> = 5 V <sub>DC</sub> , IN+/IN- Falling (Note 4) | 1.5 | 2.0  | 2.3  |       |

| V <sub>IH</sub>   | High Logic Level Input Voltage   | $V_{DRV} = 5 V_{DC}$ , IN+/IN- Rising (Note 5)                  | 2.0 | 2.2  | 2.8  | V     |

| V <sub>HYST</sub> | Input Logic Threshold Hysteresis | $V_{IH}$ Rising – $V_{IL}$ Falling                              | 0.1 | 0.18 | 0.35 |       |

| R <sub>IL</sub>   | Logic Input Pull-Down Resistance | (Note 6)                                                        |     | 5    |      | kΩ    |

### $V_{CC}$ , $V_{FB}$ and $V_{DRV}$ Static Electrical Characteristics (-55°C $\leq T_C \leq$ 110°C unless otherwise noted)

| Symbol                   | Parameter                                        | Test Conditions                                                                             | MIN  | ΤΥΡ  | MAX  | Units |  |

|--------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|------|-------|--|

| V <sub>cc</sub>          | V <sub>CC</sub> Operating Voltage Range          |                                                                                             | 9    | 10   | 11   | V     |  |

| I <sub>CC0 (sleep)</sub> | V <sub>CC</sub> Sleep Mode Quiescent Current     | $IN+=0\;V_{DC},IN-=0\;V_{DC},EN=5\;V_{DC}$                                                  | 1.5  | 2.5  | 3.5  |       |  |

| I <sub>CCQ (run)</sub>   | $V_{CC}$ Run Mode Quiescent Current              | $IN+=0 V_{DC}$ , $IN-=5 V$ , $EN=0 V$                                                       | 5.5  | 8    | 11   |       |  |

| I <sub>CC(250k)</sub>    | V <sub>CC</sub> Total Operating Current: 250 kHz | $V_{DRV} = 5 V_{DC},$<br>IN+ = 0-5V, f <sub>s</sub> = 250 kHz, 50% On-Time                  | 8    | 10   | 13   | mA    |  |

| I <sub>CC(1M)</sub>      | V <sub>CC</sub> Total Operating Current: 1 MHz   | $V_{DRV} = 5 V_{DC},$<br>IN+ = 0-5V, f <sub>s</sub> = 250 kHz, 50% On-Time                  | 16   | 20   | 23   | 23    |  |

| V <sub>DRV</sub>         | Regulated Gate Driver Voltage                    | V <sub>DRV</sub> to SS (Note 7)                                                             | 4.50 | 5.00 | 5.75 | v     |  |

| V <sub>FB</sub>          | Linear Regulator Reference Input Voltage         | V <sub>FB</sub> to SS (Note 7)                                                              | 3.33 | 3.63 | 3.93 | V     |  |

| I <sub>DRVQ</sub>        | V <sub>DRV</sub> Off State Quiescent Current     | $IN+=0\;V_{DC},IN-=0\;V_{DC},EN=0\;VDC$                                                     |      | 7    |      |       |  |

| I <sub>DRV_250kHz</sub>  | V <sub>DRV</sub> Operating Current: 250 kHz      | $V_{DRV} = 5 V_{DC},$<br>IN+ = 0-5V, f <sub>s</sub> = 250 kHz, 50% On-Time                  |      | 9    |      | mA    |  |

| I <sub>DRV_1MHz</sub>    | V <sub>DRV</sub> Operating Current: 1 MHz        | V <sub>DRV</sub> = 5 V <sub>DC</sub> ,<br>IN+ = 0-5V, f <sub>s</sub> = 250 kHz, 50% On-Time |      | 19   |      |       |  |

## **Under-Voltage Lockout Static Electrical Characteristics** (-55°C $\leq$ T<sub>C</sub> $\leq$ 125°C unless otherwise noted)

| Symbol              | Parameter                                             | Test Conditions | MIN | ΤΥΡ | MAX  | Units |

|---------------------|-------------------------------------------------------|-----------------|-----|-----|------|-------|

| UVLO+               | V <sub>DRV</sub> UVLO Rising Threshold                |                 | 2.6 | 3.6 | 4.7  |       |

| UVLO+<br>UVLO-      | V <sub>DRV</sub> UVLO Hysteresis to Falling Threshold | (Note 7)        | 0.3 | 0.4 | 0.68 | V     |

| POR <sub>(th)</sub> | POR Threshold Voltage                                 | I(PG) = 15 mA   |     |     | 0.15 |       |

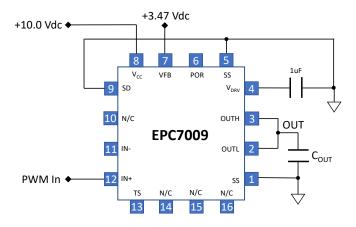

# **Power Driver Dynamic Electrical Characteristics** ( $T_C = 25^{\circ}C$ unless otherwise noted)

| Symbol              | Parameter                        | Test C                                                     | onditions                  | MIN | ТҮР | MAX | Units |

|---------------------|----------------------------------|------------------------------------------------------------|----------------------------|-----|-----|-----|-------|

| t <sub>d(on)</sub>  | IN+/INto-OUT Turn-ON Delay Time  | VDRV = 5 VDC; CC                                           | )UT = 2200 pF (See         |     | 10  |     |       |

| t <sub>d(off)</sub> | IN+/INto-OUT Turn-OFF Delay Time | Figures 2, 3, 4 and                                        | 5)                         |     | 7   |     |       |

|                     |                                  | V <sub>DRV</sub> = 5 VDC<br>(See Figures 2, 3,<br>4 and 5) | C <sub>OUT</sub> = 1000 pF |     |     |     | ns    |

| t <sub>r</sub>      | OUT Rise Time                    |                                                            | C <sub>OUT</sub> = 2200 pF |     | 3.5 |     |       |

|                     |                                  |                                                            | C <sub>OUT</sub> = 5100 pF |     |     |     | - 115 |

|                     |                                  |                                                            | C <sub>OUT</sub> = 1000 pF |     |     |     |       |

| t <sub>f</sub>      | OUT Fall Time                    |                                                            | C <sub>OUT</sub> = 2200 pF |     | 3.5 |     |       |

|                     |                                  |                                                            | C <sub>OUT</sub> = 5100 pF |     |     |     |       |

# **Dynamic Electrical Characteristics** ( $T_c = 25^{\circ}C$ unless otherwise noted)

| Symbol | Parameter                      | Test Conditions      | MIN | ΤΥΡ | MAX | Units |

|--------|--------------------------------|----------------------|-----|-----|-----|-------|

| PW     | Minimum Pulse Width, ON or OFF | $V_{DRV} = 5 V_{DC}$ | 50  |     |     | ns    |

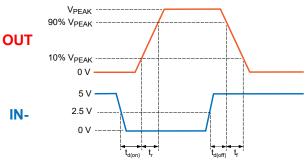

## **Switching Figures**

Only pins connected during testing identified. Pulse Generator set to 500 kHz frequency, 5% duty cycle.

NOTE: Waveforms exaggerated for clarity and observability.

Figure 3. IN+ -to-OUT Switching Time Definition

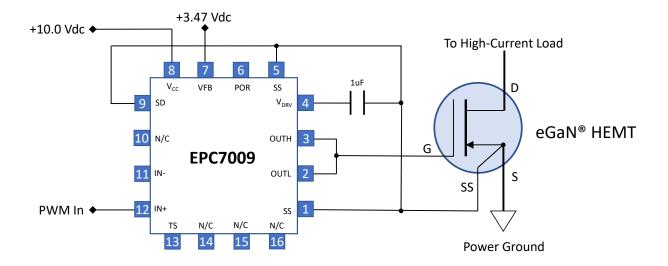

Only pins connected during testing identified. Pulse Generator set to 500 kHz frequency, 5% duty cycle.

Figure 4. IN- -to-OUT Switching Time Test Circuit

NOTE: Waveforms exaggerated for clarity and observability.

Figure 5. IN- -to-OUT Switching Time Definition

**EPC.SPACE**

## **Radiation Characteristics**

The EPC7009 is a Radiation Hardness-Assured Single Output GaN Driver Integrated Circuit.

- EPC Space's EPC7009 internally utilizes eGaN HEMT technology designed, fabricated and tested per Mil-Std-883 Method 1019 for total ionizing dose validation.

- The EPC7009 has been found to be immune to Single Event Effect and Upset when irradiated with gold ion Au at a surface LET (Si) of 84 MeV/mg/cm<sup>2</sup> at TAMU.

### **Specification Notes**

1.)  $V_{DRV} = +5 V_{DC}$ , SS = 0  $V_{DC}$ .

- 2.) Measured using 4-Wire (Kelvin) sensing techniques.

- 3.) Guaranteed by design. Not tested in production.

- 4.) When the logic input (IN+) is at the low input voltage level the OUTL output is guaranteed to be ON (~SS potential) and the OUTH output is guaranteed to be OFF (open).

- 5.) When the logic input (IN+) is at the high input voltage level the OUTH output is guaranteed to be ON (~V<sub>DRV</sub> potential) and the OUTL output is guaranteed to be OFF (open).

- 6.) Pull-down to SS for IN+ and pull-up to  $V_{DRV}$  for IN-.

- 7.) The regulated output voltage,  $V_{DRV}$ , is 1.44 x  $V_{FB}$ , nominal. For a nominal 5  $V_{DC}$  output for  $V_{DRV}$ ,  $V_{FB} = 3.47 V_{DC}$ . The gate driver potential  $V_{DRV}$  may be adjusted to any value within the  $V_{FB}$  specified range.

### **EPC7009 Operational Truth Table**

The truth table for the logic inputs and the power supply UVLO circuit is shown in the following table. In the following table, OUT is the combined driver output when OUTL and OUTH are connected together.

All conditions in the table are valid when  $V_{BIAS}$  and  $V_{DRV}$  are greater than UVLO+. When  $V_{CC}$  and  $V_{DRV}$  are less than ULVO+ rising or UVLO+ falling, OUT is in the low (L) state, approximately the SS potential, regardless of the state of either logic input.

| IN+ | IN- | OUT |

|-----|-----|-----|

| 0   | 0   | L   |

| 1   | 0   | Н   |

| 0   | 1   | L   |

| 1   | 1   | L   |

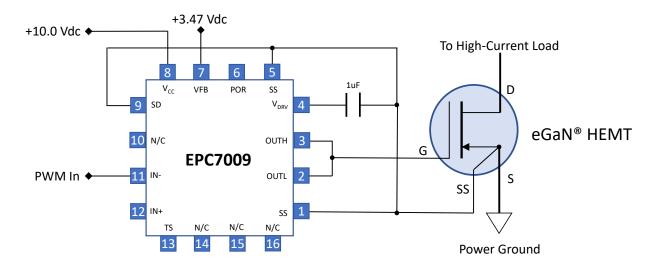

## **Application Information**

The following figures detail the suggested applications for the EPC7009 integrated circuit. For all applications, please refer to the following sections for proper power supply bypassing and layout recommendations and criteria.

In all the following figures, only the pins that are considered or that require connection are identified.

Note: Keep Out-to-Gate and SS-to-Source-Sense connections as short as possible.

Figure 7. Non-Inverting Mode Low-Side Driver and EPC Space eGaN® HEMT

Note: Keep Out-to-Gate and SS-to-Source-Sense connections as short as possible. *Figure 8. Inverting Mode Low-Side Driver and EPC Space eGaN® HEMT*

**EPC.SPACE**

Note: Make all OUTH-to-RG1, OUTL-to-RG2, the tie point of RG1/RG2-to-Gate and SS-to-Source Sense connections of equal length and as short as possible. RG1/RG2 are 20  $\Omega$ , maximum

Figure 9. Non-Inverting Mode Low-Side Driver and EPC Space eGaN<sup>®</sup> HEMT with Gate Damping/Slow-Down Resistors

In Figure 9 resistor RG1 is used to control the rise time of the eGaN<sup>®</sup> HEMT and resistor RG2 is used to control the fall time. Such resistors are often utilized to reduce EMI or to minimize voltage overshoot and ringing on the V<sub>DD</sub> bus local to the high current being switched by the eGaN HEMT.

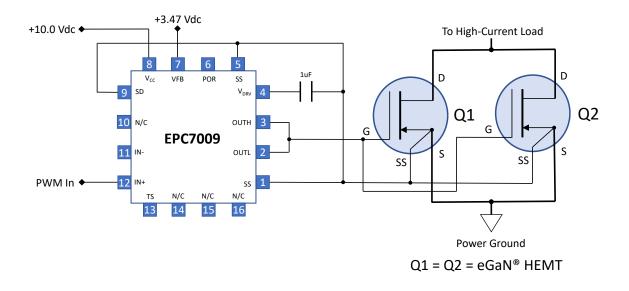

Note: Make all OUTH/OUTL-to-Gate, SS-to-Source Sense and Source connections as short as possible. Also keep the Drain connections as short as physically possible.

Figure 10. Non-Inverting Mode Low-Side Driver Driving Multiple, Parallel EPC Space eGaN® HEMTs

For parallel the parallel HEMT configuration as shown in Figure 10, the number of HEMT devices that may be driven in parallel is determined by the  $C_{ISS}$  of the individual HEMTs and the capacitive drive capability of the EPC7009 gate driver integrated circuit.

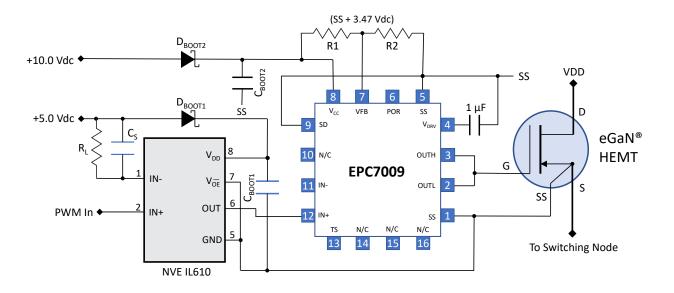

Note: Make all OUTH/OUTL-to-Gate, SS-to-Source Sense and Source connections as short as possible. Also keep the Drain connections as short as physically possible. The SS node may be treated as a local etch plane in the area of the IL610, the EPC7009 and the eGaN® HEMT. Circuit shown utilizes dual bootstrapping: one for the NVE IL610 and one for the EPC7009.

Figure 11. Non-Inverting Mode Low-Side Driver Driving Multiple, Parallel EPC Space eGaN® HEMTs

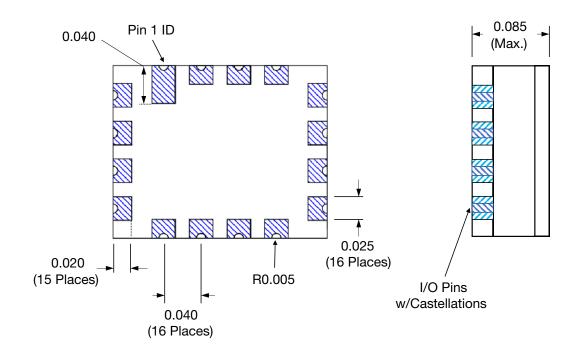

## **Package Outline Dimensions**

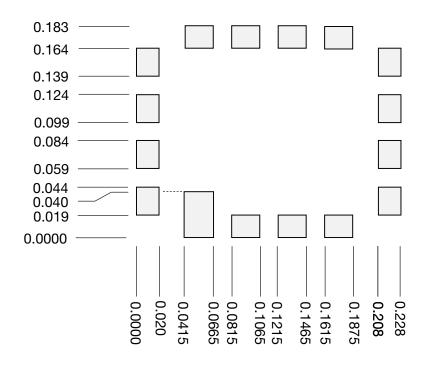

Figure 12. EPC7009L16SH Package Outline Dimensions

## **Recommended PCB Solder Pad Configuration**

To prevent damage to the internal circuitry it is important that the EPC7009L16SH integrated circuit be soldered to the PCB motherboard using SN63 (or equivalent) solder. The recommended PCB pad dimensions and locations are shown in Figure 13.

All dimensions are shown in inches.

Figure 13. Recommended PCB Solder Pad Configuration (Top View)

### **Disclaimers**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE. EPC Space Corporation, its affiliates, agents, employees, and all persons acting on its or their behalf (collectively, "EPC Space"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product. EPC Space makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose. To the maximum extent permitted by applicable law. EPC Space disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability. Statements regarding the suitability of products for certain types of applications are based on EPC Space market knowledge of typical requirements that are often placed on similar technologies in generic applications. Product specifications do not expand or otherwise modify EPC Space terms and conditions of purchase, including but not limited to the warranty expressed therein. Except as expressly indicated in writing, EPC Space products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the EPC Space product could result in personal injury or death. Customers using EPC Space products not expressly indicated for use in such applications do so at their own risk. Please contact authorized EPC Space personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of EPC Space. Product names and markings noted herein may be trademarks of their respective owners.

#### **Export Administration Regulations (EAR)**

The products described in this datasheet are subject to the U.S. Export Administration Regulations (EAR), 15 C.F.R. Pts 730-774, and are classified in ECCN 9A515.e. These products may not be exported, reexported, or transferred (in country) to any foreign country, or foreign entity, by any means, except in accordance with the requirements of such regulations.

#### Patents

EPC Corporation and EPC Space hold numerous worldwide patents. Any that apply to the product(s) listed in this document are identified by markings on the product(s) or on internal components of the product(s) in accordance with local patent laws.

eGaN<sup>®</sup> is a registered trademark of Efficient Power Conversion Corporation, Inc. Data and specification subject to change without notice.

### **Revisions**

| Datasheet Revision | Product Status                     |

|--------------------|------------------------------------|

| REV P#             | Proposal/development               |

| REV Q#             | Characterization and Qualification |

|                    | Production Released                |

Information subject to change without notice. Revised April, 2024