Revised October 20, 2025

#### **Features**

- 100 V

- Low R<sub>DS(on)</sub>

- 3 x 5 mm QFN package

- Exposed top for top-side thermal management

- Moisture rating MSL2

- Enhanced thermal-max package

- Single Event Effect (SEE) Hardened SEE immunity up to LET of 37 MeV/(mg/cm²) in Si with V<sub>DS</sub> up to 80% of rated breakdown

## **Applications**

- · Satellite and avionics

- Deep space probes

- 24 V-60 V motor drives

- High speed DC-DC conversion

- Motor controllers

#### **Benefits**

- Ultra high efficiency

- No reverse recovery

- Ultra low Q<sub>G</sub>

- Small footprint

- Excellent thermal

# **Application Notes**

- Easy-to-use and reliable gate, Gate Drive ON = 5 V typical, OFF = 0 V (negative voltage not needed)

- Top of FET is electrically connected to source

#### **Thermal Characteristics**

| Symbol                 | Parameter-Conditions                                            | Value | Units |

|------------------------|-----------------------------------------------------------------|-------|-------|

| $R_{\theta JC}$        | Thermal Resistance, Junction-to-Case (Case TOP)                 | 0.2   |       |

| $R_{\theta JB}$        | Thermal Resistance, Junction-to-Board (Case BOTTOM)             | 1.5   |       |

| $R_{\theta JA\_JEDEC}$ | Thermal Resistance, Junction-to- Ambient (using JEDEC 51-2 PCB) | 45    | °C/W  |

| R <sub>0JA_EVB</sub>   | Thermal Resistance, Junction-to- Ambient (using EPC90142 EVB)   | 21    |       |

eGaN<sup>®</sup> FET in a Plastic Surface Mount 100 V, 133 A, 1.8 mΩ

## **Description**

The EPCS5001PA is a commercial plastic 3 x 5 mm QFN package with an exposed top for excellent thermal management. It is tailored to high frequency DC-DC applications to/from 40 V-60 V and 48 V BLDC motor drives.

The part has three variants:

- **1. EPCS5001PAC:** COTS, with electrical screening at EPCS and visual inspection

- 2. EPCS5001PAV: TXV space-level screened part

- 3. EPCS5001PAS: Full S-level screened part

The thermal resistance to case top is ~0.2 °C/W, resulting in excellent thermal behavior and easy cooling. The device features an enhanced PQFN "Thermal-Max" package. The exposed top enhances top-side thermal management and the side-wettable flanks guarantee that the complete side-pad surface is wetted with solder during the reflow soldering process, which protects the copper and allows soldering to occur on this external flank area for easy optical inspection.

Compared to a Si MOSFET, the footprint of 15 mm² is less than half of the size of the best-in-class Si MOSFET with similar  $R_{\rm DS(on)}$  and voltage rating,  $Q_{\rm G}$  and  $Q_{\rm GD}$  are significantly smaller and  $Q_{\rm RR}$  is 0. This results in lower switching losses and lower gate driver losses. Moreover, EPCS5001PA is very fast and can operate with deadtime less than 10 ns for higher efficiency and  $Q_{\rm RR}=0$  is a big advantage for reliability and EMI. In summary, EPCS5001PA allows the highest power density due to enhanced efficiency, smaller size, and higher switching frequency for smaller inductor and fewer capacitors.

The EPCS5001PA enables designers to improve efficiency and save space. The excellent thermal behavior enables easier and lower cost cooling. The ultra-low capacitance and zero reverse recovery of the eGaN® FET enables efficient operation in many topologies. Performance is further enhanced due to the small, low inductance footprint.

#### **Maximum Rating**

| Symbol              | Parameter-Conditions                              | Value      | Units |  |

|---------------------|---------------------------------------------------|------------|-------|--|

| V <sub>DS</sub>     | Drain-to-Source Voltage (Note 1)                  | 100        | V     |  |

| V <sub>DS(tr)</sub> | Drain-to-Source Voltage (Repetitive Transient)(1) | 120        | V     |  |

|                     | Continuous ( $T_J \le 125$ °C)                    | 133        |       |  |

| I <sub>D</sub>      | Pulsed (25°C, T <sub>PULSE</sub> = 300 μs)        | 408        | A     |  |

| V <sub>GS</sub>     | Gate-to-Source Voltage (Note 2)                   | +6 / -4    | V     |  |

| T <sub>J</sub>      | Operating Temperature -40 to 150                  |            | °C    |  |

| T <sub>STG</sub>    | Storage Temperature                               | -55 to 175 | - °C  |  |

$<sup>^{(1)}</sup>$  Pulsed repetitively, duty cycle factor (DC  $_{Factor}) \leq 1\%;$

See Figure 13 and Reliability Report Phase 16, Section 3.2.6

## Static Characteristics ( $T_J = 25^{\circ}$ C unless otherwise noted)

| Parameter                              | Symbol              | Symbol Test Conditions                         |     | TYP  | MAX | Units |  |

|----------------------------------------|---------------------|------------------------------------------------|-----|------|-----|-------|--|

| Drain to Source Voltage                | B <sub>VDSS</sub>   | $V_{GS} = 0 V$                                 | 100 |      |     | V     |  |

| Drain to Source Leakage                | I <sub>DSS</sub>    | $V_{DS} = 100 \text{ V}, V_{GS} = 0 \text{ V}$ |     | 1    | 100 | μA    |  |

| Gate to Source Forward Leakage         |                     | V <sub>GS</sub> = 5 V                          |     | 0.01 | 4   |       |  |

| Gate to Source Forward Leakage         | I <sub>GSS</sub>    | V <sub>GS</sub> = 5 V, T <sub>J</sub> = 125°C  |     | 0.4  | 9   | mA    |  |

| Gate to Source Reverse Leakage         |                     | V <sub>GS</sub> = -4 V                         |     | 0.01 | 0.2 |       |  |

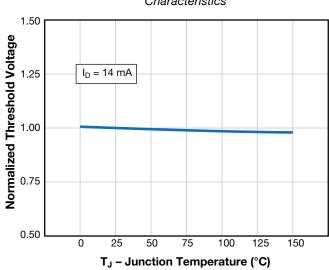

| Gate Threshold Voltage                 | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}$ , $I_D = 14$ mA              | 0.8 | 1.3  | 2.5 | V     |  |

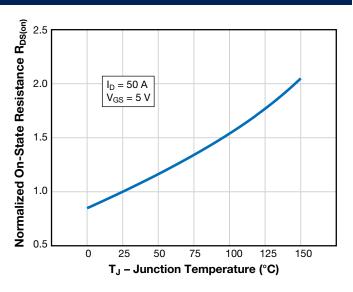

| Drain to Source On Resistance (Note 3) | R <sub>DS(on)</sub> | $V_{GS} = 5 \text{ V}, I_{D} = 50 \text{ A}$   |     | 1.4  | 1.8 | mΩ    |  |

| Source to Drain Forward Voltage        | V <sub>SD</sub>     | $I_S = 0.5 \text{ A}, V_{GS} = 0 \text{ V}$    |     | 1.5  | 3   | V     |  |

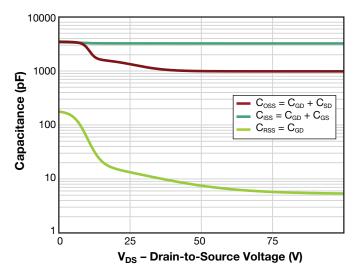

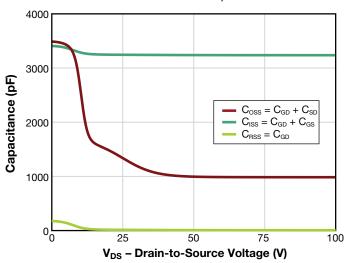

# **Dynamic Characteristics**# (*T<sub>J</sub>* = 25°C unless otherwise noted)

| Parameter                                             | Symbol               | Test Conditions                                                                             | MIN | TYP  | MAX  | Units |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------|-----|------|------|-------|

| Input Capacitance                                     | C <sub>ISS</sub>     |                                                                                             |     | 3200 | 4800 |       |

| Reverse Transfer Capacitance                          | C <sub>RSS</sub>     | $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$                                               |     | 7    |      |       |

| Output Capacitance                                    | C <sub>OSS</sub>     |                                                                                             |     | 1000 | 1200 | pF    |

| Effective Output Capacitance, Energy Related (Note 4) | C <sub>OSS(ER)</sub> | $V_{DS} = 0$ to 50 V, $V_{GS} = 0$ V                                                        |     | 1300 |      |       |

| Effective Output Capacitance, Time Related (Note 5)   | C <sub>OSS(TR)</sub> |                                                                                             |     | 1700 |      |       |

| Gate Resistance (Note 6)                              | $R_{G}$              |                                                                                             |     | 0.5  |      | Ω     |

| Total Gate Charge (Note 6)                            | $Q_{G}$              | $V_{DS} = 50 \text{ V}, V_{GS} = 5 \text{ V}, I_{D} = 50 \text{ A}$                         |     | 23   | 29   |       |

| Gate to Source Charge (Note 7)                        | Q <sub>GS</sub>      |                                                                                             |     | 8.9  |      |       |

| Gate to Drain Charge (Note 7)                         | $Q_{GD}$             | $V_{DS} = 50 \text{ V}, I_{D} = 50 \text{ A}$ $V_{DS} = 50 \text{ V}, V_{GS} = 0 \text{ V}$ |     | 2.3  |      |       |

| Gate Charge at Threshold (Note 7)                     | Q <sub>G(TH)</sub>   |                                                                                             |     | 6.3  |      | nC    |

| Output Charge (Note 6)                                | Q <sub>oss</sub>     |                                                                                             |     | 85   | 94   |       |

| Source to Drain Recovery Charge (Note 6)              | Q <sub>RR</sub>      |                                                                                             |     | 0    |      |       |

All measurements were done with substrate connected to source.

#### **Radiation Characteristics**

EPC Space eGaN<sup>®</sup> HEMTs are tested according to MIL-STD-750 Method 1019 for total ionizing dose validation. Every manufacturing lot is tested for total ionizing dose of 1 Mrad of Gamma radiation exposure with an in-situ bias for the following conditions:

$\begin{array}{ll} \text{ON} & \mid V_{\text{GS}} = 5 \text{ V} \\ \text{NO BIAS} & \mid V_{\text{DS}} = V_{\text{GS}} = 0 \text{ V} \\ \text{OFF} & \mid V_{\text{DS}} = 80\% \text{ B}_{\text{VDSS}} \end{array}$

## Electrical Characteristics up to 1000 krads ( $T_C = 25^{\circ}$ C unless otherwise noted. Typical (TYP) values are for reference only.)

| Parameter                        | Symbol              | Test Conditions                                | MIN | TYP    | MAX | Units |

|----------------------------------|---------------------|------------------------------------------------|-----|--------|-----|-------|

| Maximum Drain to Source Voltage  | V <sub>DSMAX</sub>  | $V_{GS} = 0 V$                                 | 100 |        |     | V     |

| Gate to Source Threshold Voltage | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}$ , $I_{D} = 18 \text{ mA}$    | 0.8 | 1.3    | 2.5 | V     |

| Drain to Source Leakage          | I <sub>DSS</sub>    | V <sub>DS</sub> = 100 V, V <sub>GS</sub> = 0 V |     | 0.0001 | 0.1 |       |

| Gate to Source Forward Leakage   |                     | $V_{GS} = 6 \text{ V}$                         |     | 0.01   | 4   | mA    |

| Gate to Source Reverse Leakage   | IGSS                | V <sub>GS</sub> = -4 V                         |     | 0.01   | 0.2 |       |

| Drain to Source Resistance       | R <sub>DS(on)</sub> | $I_D = 80 \text{ A}, V_{GS} = 5 \text{ V}$     |     | 1.4    | 1.8 | mΩ    |

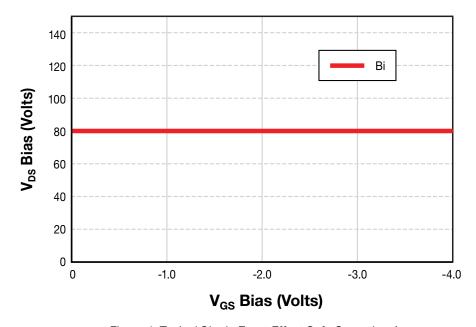

## **Typical Single Event Effect Safe Operating Area**

Note: All Radiation Single Event Effects testing are performed in heavy ion environments such as the K-500 Cyclotron at Texas A&M.

| Test    |     | Enviro                               | V <sub>DS</sub> Vol       | tage ( V)                 |                       |                |

|---------|-----|--------------------------------------|---------------------------|---------------------------|-----------------------|----------------|

| See SOA | lon | LET<br>MeV/(mg/cm²) in Si<br>(+/-5%) | Range<br>µm<br>(+/- 7.5%) | Energy<br>MeV<br>(+/-10%) | V <sub>GS</sub> = 0 V | $V_{GS} = -4V$ |

|         | Bi  | 37                                   | 71.3                      | 147                       | 80                    | 80             |

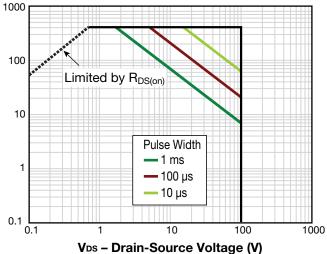

Figure 1: Typical Single Event Effect Safe Operating Area

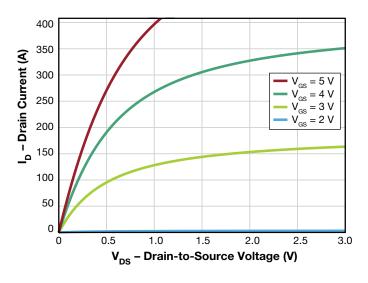

Figure 2: Typical Output Characteristics at 25°C

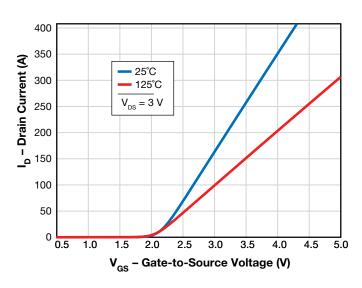

Figure 3: Typical Transfer Characteristics

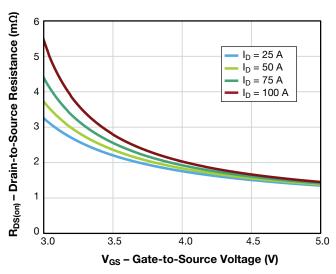

Figure 4: Typical  $R_{\mathrm{DS}(on)}$  vs.  $V_{\mathrm{GS}}$  for Various Drain Currents

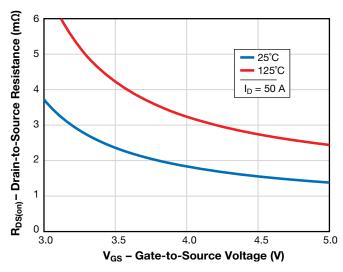

Figure 5: Typical  $R_{DS(on)}$  vs.  $V_{GS}$  for Various Temperatures

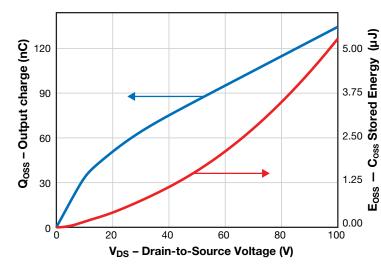

Figure 6: Typical Output Charge and  $C_{

m OSS}$  Stored Energy

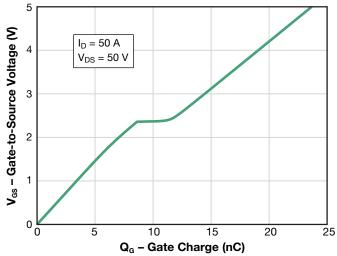

Figure 7: Typical Gate Charge

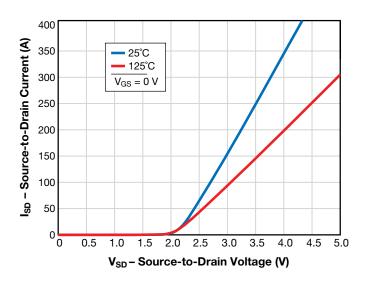

Figure 8: Typical Reverse Drain-Source Characteristics

Figure 10: Typical Normalized Threshold Voltage vs. Temperature

Figure 12: Typical Capacitance (Log Scale)

Figure 9: Typical Normalized On-State Resistance vs. Temperature

Figure 11: Typical Capacitance (Linear Scale)

$V_{DS}$  – Drain-Source Voltage (V)  $T_{J}$  = Max Rated,  $T_{C}$  = +25°C, Single Pulse

Figure 13: Safe Operating Area

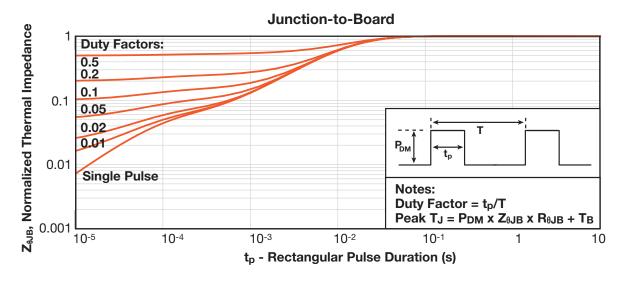

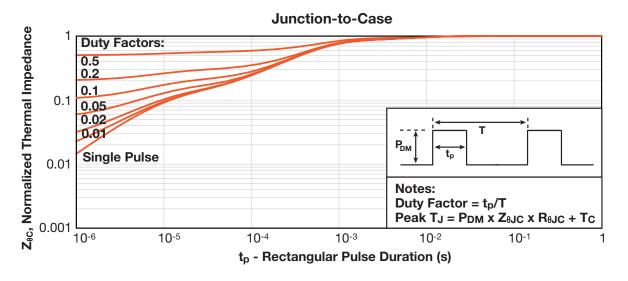

Figure 14: Typical Transient Thermal Response Curves

Figure 15: Typical Transient Thermal Response Curves

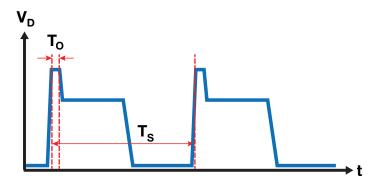

1% is the ratio between T<sub>0</sub> (overvoltage duration) and T<sub>s</sub> (one switching period).

Figure 16: Duty Cycle Factor (DC<sub>Factor</sub>) Illustration for Repetitive Overvoltage Specification

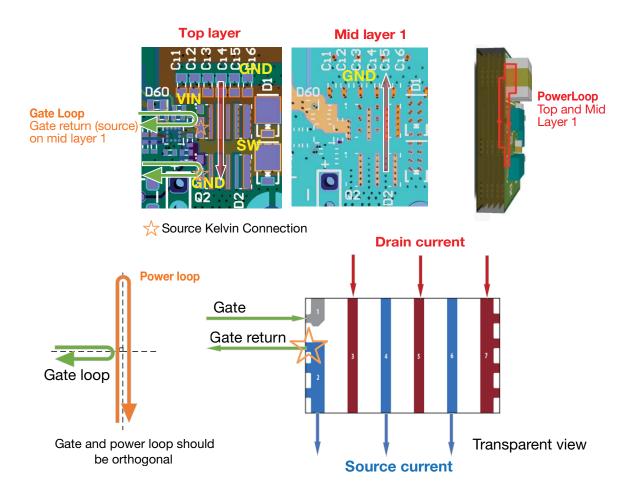

## **Layout Characteristics**

GaN transistors generally behave like power MOSFETs, but at much higher switching speeds and power densities, therefore layout considerations are very important, and care must be taken to minimize layout parasitic inductances. The recommended design utilizes the first inner layer as a power loop return path. This return path is located directly beneath the top layer's power loop allowing for the smallest physical loop size. This method is also commonly referred to as flux cancellation. Variations of this concept can be implemented by placing the bus capacitors either next to the high side device, next to the low side device, or between the low and high side devices, but in all cases the loop is closed using the first inner layer right beneath the devices.

A similar concept is also used for the gate loop, with the return gate loop located directly under the turn ON and OFF gate resistors.

Furthermore, to minimize the common source inductance between power and gate loops, the power and gate loops are laid out perpendicular to each other, and a via next to the source pad closest to the gate pad is used as Kelvin connection for the gate driver return path.

The EPC90133 – 100 V, 40 A Half-Bridge Development Board Featuring EPC2302 implements our recommended vertical inner layout.

Figure 17: Inner Vertical Layout for Power and Gate Loops from EPC90133

Detailed recommendations on layout can be found on EPC's website: Optimizing PCB Layout with eGaN FETs.pdf

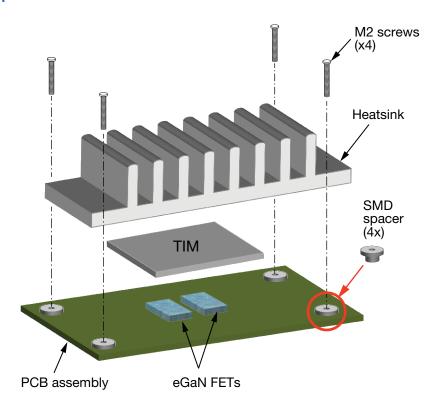

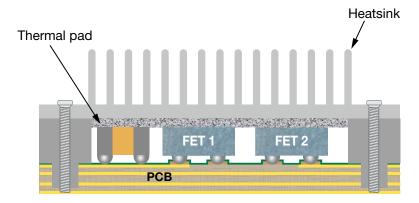

## **Typical Thermal Concept**

The EPCS5001PA can take advantage of dual sided cooling to maximize its heat dissipation capabilities in high power density designs. *Note that the top of EPC FETs are connected to source potential, so for half-bridge topologies the Thermal Interface Material (TIM)* needs to provide electrical isolation to the heatsink.

Recommended best practice thermal solutions are covered in detail in How2AppNote012 - How to Get More Power Out of an eGaN Converter.pdf.

Figure 18: Exploded view of heatsink assembly using screws

Figure 19: A cross-section image of dual sided thermal solution

Note: Connecting the heatsink to ground is recommended and can significantly improve radiated EMI

The thermal design can be optimized by using the GaN FET Thermal Calculator on EPC's website.

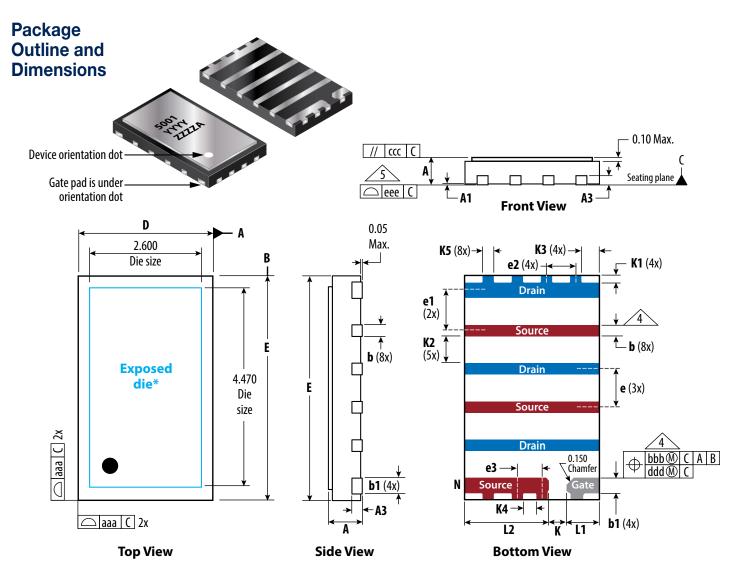

\*The exposed die is the silicon substrate that is internally connected to the source. It is not recommended to use it as an electrical connection

| Symbol     | Dime     | Note     |       |      |

|------------|----------|----------|-------|------|

| Syllibol   | MIN      | NOM      | MAX   | Note |

| Α          | 0.60     | 0.65     | 0.70  |      |

| <b>A</b> 1 | 0.00     | 0.02     | 0.05  |      |

| А3         |          |          | 0.25  |      |

| b          | 0.20     | 0.25     | 0.30  | 4    |

| b1         | 0.30     | 0.35     | 0.40  | 4    |

| D          | 2.90     | 3.00     | 3.10  |      |

| Е          | 4.90     | 5.00     | 5.10  |      |

| е          | 0        | .85 BS   | С     |      |

| <b>e1</b>  | 0        | .90 BS   | С     |      |

| e2         | 0        | 0.65 BSC |       |      |

| <b>e</b> 3 | 0.55 BSC |          |       |      |

| L1         | 0.625    | 0.725    | 0.825 |      |

| L2         | 1.775    | 1.875    | 1.975 |      |

| Symbol     | Dim | ension ( | (mm) | Note |  |  |  |

|------------|-----|----------|------|------|--|--|--|

| Syllibol   | MIN | NOM      | MAX  | Note |  |  |  |

| K          |     | 0.40 Re  | f    |      |  |  |  |

| <b>K</b> 1 |     | 0.15 Re  | f    |      |  |  |  |

| K2         |     | 0.60 Re  | f    |      |  |  |  |

| К3         |     | 0.40 Re  | f    |      |  |  |  |

| K4         | (   | 0.30 Ref |      |      |  |  |  |

| <b>K</b> 5 |     |          |      |      |  |  |  |

| aaa        |     |          |      |      |  |  |  |

| bbb        |     |          |      |      |  |  |  |

| ccc        |     |          |      |      |  |  |  |

| ddd        |     |          |      |      |  |  |  |

| eee        |     |          |      |      |  |  |  |

| N          |     | 7        |      | 3    |  |  |  |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5-2009

- 2. All dimensions are in millimeters

- 3. N is the total number of terminals

- Dimension b applies to the metalized terminal and a radius on the other end of it, dimension b should not be measured in that radius area.

- Ć Coplanarity applies to the terminals and all the other bottom surface metallization.

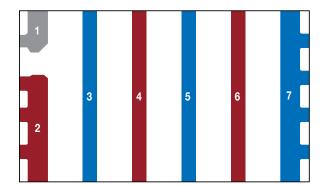

#### TRANSPARENT VIEW

| PIN | Description |  |  |  |

|-----|-------------|--|--|--|

| 1   | Gate        |  |  |  |

| 2   | Source      |  |  |  |

| 3   | Drain       |  |  |  |

| 4   | Source      |  |  |  |

| 5   | Drain       |  |  |  |

| 6   | Source      |  |  |  |

| 7   | Drain       |  |  |  |

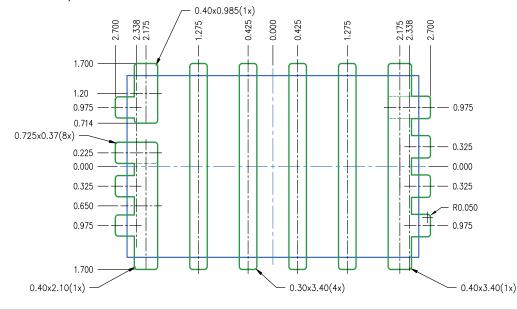

#### RECOMMENDED SOLDER MASK PATTERN

(units in mm)

# Legend:

Part outline Mask Opening

Radius = 0.05

Land pattern is solder mask defined.

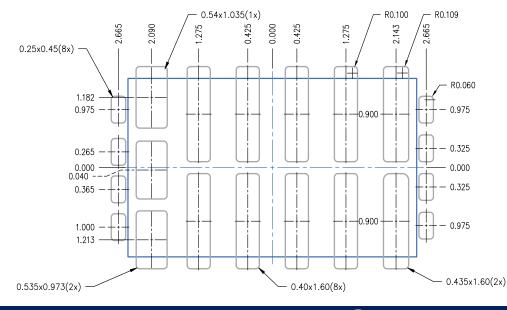

#### RECOMMENDED STENCIL DRAWING

(units in mm)

# Legend: Part outline Stencil opening

Recommended stencil should be 4 mil (100  $\mu$ m) thick, must be laser cut, openings per drawing. Intended for use with SAC305 Type 4 solder, reference 88.5% metals content.

The corner has a radius of R60.

EPC has tested this stencil design and not found any scooping issues.

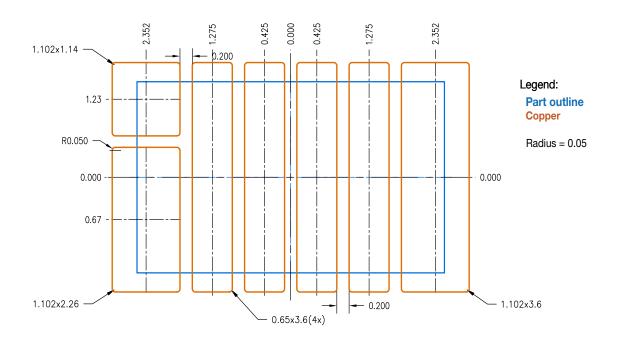

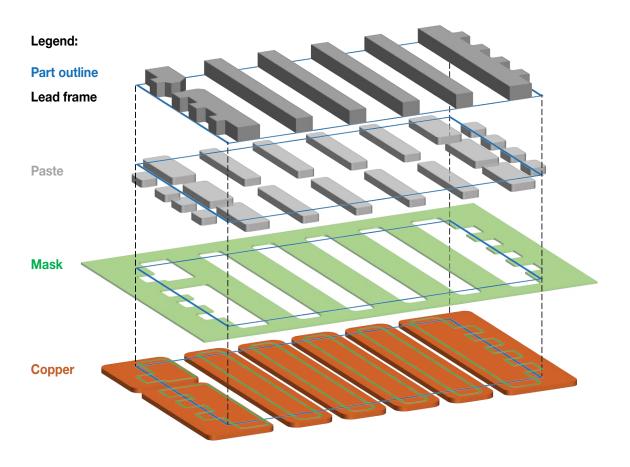

## **RECOMMENDED COPPER DRAWING**

(units in mm)

# **3D Composite**

- Note 1. Never exceed the absolute maximum V<sub>DS</sub> of the device otherwise permanent damage/destruction may result.

- Note 2. Never exceed the absolute maximum  $V_{GS}$  of the device otherwise permanent damage/destruction may result. We recommend a  $V_{GS}$  of 5 V for optimum operation across life and radiation.

- Note 3. Measured using four wire (Kelvin) sensing and pulse measurement techniques. Measurement pulse width is 80 µs and duty cycle is 1%, maximum.

- Note 4.  $C_{OSS(ER)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>.

- Note 5.  $C_{OSS(TR)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{DS}$  is rising from 0 to 50% BV<sub>DSS</sub>.

- Note 6. Guaranteed by design/device construction. Not Tested.

- Note 7. The gate charge parameters are measured based on the MIL-STD-750.3471 Condition B. A high speed constant gate current ( $I_{const}$ ) is provided to the Gate of the DUT during the time that the ground switch ( $G_{\rm S}$ ) is OFF ( $t_{off}$ ). The DUT is switched ON and OFF using ground-sensed switch  $G_{\rm S}$ . The gate current is adjusted to yield the desired charge per unit time ( $I_{const}$  · time per division) on the measuring oscilloscope. The  $G_{\rm S}$  pulse drive ON time ( $t_{on}$ ) is adjusted for the desired observability of the gate-source voltage ( $V_{\rm GS}$ ) waveform. The maximum duty cycle of the ground switch ( $t_{off}/t_{on}$ ) should be set to 1% maximum. Please note that all gate-related signals are referenced to the "Source Sense" pin on the package. At all times during the measurement, the maximum gate-source voltage is clamped to 5  $V_{\rm DC}$ .

#### **Disclaimers**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE. EPC Space Corporation, its affiliates, agents, employees, and all persons acting on its or their behalf (collectively, "EPC Space"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product. EPC Space makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose. To the maximum extent permitted by applicable law, EPC Space disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability. Statements regarding the suitability of products for certain types of applications are based on EPC Space market knowledge of typical requirements that are often placed on similar technologies in generic applications. Product specifications do not expand or otherwise modify EPC Space terms and conditions of purchase, including but not limited to the warranty expressed therein. Except as expressly indicated in writing, EPC Space products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the EPC Space product could result in personal injury or death. Customers using EPC Space products not expressly indicated for use in such applications do so at their own risk. Please contact authorized EPC Space personnel to obtain written terms and conditions regarding products designed for such applications. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of EPC Space. Product names and markings noted herein may be trademarks of their respective owners.

**Export Classification: EAR 99**

#### **Patents**

EPC Corporation and EPC Space hold numerous worldwide patents. Any that apply to the product(s) listed in this document are identified by markings on the product(s) or on internal components of the product(s) in accordance with local patent laws.

eGaN® is a registered trademark of Efficient Power Conversion Corporation, Inc. Data and specification subject to change without notice.

Information subject to change without notice.